Адрес на шину isa

Шина ISA

Страница 4. Описание сигналов на шине ISA

4. Описание сигналов на шине ISA

В этой главе описываются все сигналы на шине ISA. Для лучшего понимания функционирования шины целесообразно разбить все сигналы на 7 групп: АДРЕСА, ДАННЫЕ, СИНХРОСИГНАЛЫ, КОМАНДНЫЕ СИГНАЛЫ, СИГНАЛЫ РЕЖИМА ПДП, ЦЕНТРАЛЬНЫЕ СИГНАЛЫ УПРАВЛЕНИЯ, СИГНАЛЫ ПРЕРЫВАНИЯ, ПИТАНИЕ. Информация о направленности сигналов (вход, выход или двунаправленный) приводится относительно задатчика на шине.

4.1. Сигналы адреса

SA [8] [8/16]

Адресные сигналы этого типа поступают на шину с регистров адреса, в которых адрес «защелкивается». Сигналы SA позволяют осуществлять доступ к памяти только в младшем мегабайте адресного пространства. При доступе к устройству ввода/вывода только сигналы SA имеют действительное значение, а состояние сигналов SA не определено.

Во время выполнения циклов регенерации адреса только сигналы SA имеют действительное значение, а состояние сигналов SA неопределено и эти выводы должны быть в третьем состоянии для всех устройств на шине.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Внешняя плата, ставшая задатчиком на шине, должна разрешать сигнал -REFRESH для регенерации памяти, при этом внешняя плата должна перевести свои выходные формирователи сигналов адреса в третье состояние.

LA [8/16]

Сигналы этого типа поступают на шину без «защелкивания» в регистрах. Когда центральный процессор является задатчиком на шине, то значения сигналов на линиях LA истинны во время выработки сигнала BALE и они могут иметь произвольное значение в конце цикла доступа. Если задатчиком на шине является контроллер ПДП, сигналы LA истинны до начала сигнала -MEMR или -MEMW и сохраняются до конца цикла. При выполнении циклов доступа к памяти сигналы LA всегда истинны, а при доступе к устройствам ввода/вывода эти сигналы имеют уровень логического «0».

При выполнении циклов регенерации состояние линий LA неопределено и все ресурсы на шине должны поддерживать свои выходы по этим линиям в третьем состоянии.

РЕКОМЕНДАЦИИ: Для «защелкивания» сигналов LA следует использовать только регистры с потенциальным входом. Это вызвано тем, что в этом случае новый истинный адрес появится на выходе регистра по началу сигнала BALE (а не по его заднему фронту) и, кроме этого, во время циклов доступа к памяти каким-либо другим задатчиком, а не ЦП, сигнал BALE поддерживается в состоянии логической «1» и регистр с потенциальным входом станет просто повторителем сигналов LA (что и требуется в таком случае).

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата является задатчиком на шине, то сигналы LA должны быть истинны до начала сигнала -MEMR или -MEMW и сохраняться таковыми до завершения цикла. Если внешняя плата разрешает сигнал -REFRESH (следует помнить, что внешняя плата может это сделать, только будучи задатчиком на шине), то вырабатывать сигналы адреса будет контроллер регенерации, поэтому внешней плате следует перевести свои адресные выходы в третье состояние.

-SBHE

Сигнал -SBHE не вырабатывается контроллером регенерации при захвате им шины, так как никаких перестановок байтов нет и нет реального чтения данных.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если внешняя плата становится задатчиком на шине, то она должна вырабатывать сигнал -SBHE так же как центральный процессор.

Если внешняя плата, являющаяся задатчиком на шине, вырабатывает сигнал -REFRESH, то ее выход сигнала -SBHE должен быть переведен в третье состояние.

BALE [8] [8/16]

При захвате шины контроллером ПДП сигнал BALE всегда равен логической «1» (вырабатывается на материнской плате), так как сигналы LA и SA истинны до выработки командных сигналов. Если контроллер регенерации становится задатчиком на шине, то на линии BALE также поддерживается уровень логической единицы, поскольку сигналы адреса SA истинны до начала командных сигналов.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

При захвате шины внешней платой сигнал BALE поддерживается материнской платой в состоянии логической «1» на все время захвата шины. Адресные сигналы LA и SA должны быть при этом истинны в течении времени разрешения платой командных сигналов.

Если центральный процессор является задатчиком на шине и выполняет цикл доступа к ресурсу на внешней плате, то сигналы LA истинны только в течении короткого времени, поэтому сигнал BALE должен быть использован для «защелкивания» адреса в регистре. При захвате шины любым устройством, кроме ЦП, на линии BALE поддерживается уровень логической «1».

AEN [8] [8/16]

Этот сигнал запрещается, если задатчиком на шине является центральный процессор или контроллер регенерации.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

SD и SD

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Если сигнал — REFRESH разрешен, то внешние платы должны перевести свои выходы по шине данных в третье состояние, так как нет пересылок данных во время циклов регенерации памяти.

Шина ISA (Industrial Standard Architecture)

Устройства, подключенные к шине, делятся на две основных категории — bus masters и bus slaves. Bus masters — это устройства, способные управлять работой шины, т.е инициировать запись/чтение и т.д. Bus slaves — соответственно, устройства, которые могут только отвечать на запросы. Правда, есть еще «интеллектуальные слуги» (intelligent slaves), но мы их пока для ясности замнем. Ну вот, собственно, и все, что нужно знать про шины для того, чтобы понять, о чем пойдет речь дальше.

Компания IBM в 1981 представила новую шину для использования в компьютерах серии PC/XT. Шина была крайне проста по дизайну, содержала 53 сигнальных линии и 8 линий питания и представляла собой синхронную 8-битную шину с контролем четности и двухуровневыми прерываниями (trigger-edge interrupts), при использовании которых устройства запрашивают прерывания, изменяя состояние линии соответствующего IRQ с 0 на 1 или обратно. Такая организация запросов прерываний позволяет использовать каждое прерывание только одному устройству. Кроме того, шина не поддерживала дополнительных bus masters, и единственными устройствами, управляющими шиной, были процессор и контроллер DMA на материнской плате.

62-контактный слот включал 8 линий данных, 20 линий адреса (А0-А19), 6 линий запроса прерываний (IRQ2-IRQ7). Таким образом, объем адресуемой памяти составлял 1 Мбайт, и при частоте шины 4.77 МГц пропускная способность достигала 1.2 Мбайта/сек.

Забавно, что IBM не опубликовала полного описания шины с временными диаграммами сигналов на линиях данных и адреса, поэтому первым разработчикам плат расширения пришлось изрядно потрудиться. Для особо любопытных предоставляется возможность познакомиться с этой информацией.

Реализация bus mastering не была особенно удачной, поскольку, например, запрос на освобождение шины (‘Bus hang-off’) к текущему bus master обрабатывался несколько тактов, к тому же каждый master должен был периодически освобождать шину, чтобы дать возможность провести обновление памяти (memory refresh), или сам проводить обновление. Для обеспечения обратной совместимости с 8-битными платами большинстиво новых возможностей было реализовано путем добавления новых линий. Так как АТ был построен на основе процессора Intel 80286, который был существенно быстрее, чем 8088, пришлось добавить генератор состояний ожидания (wait-state generator). Для обхода этого генератора используется свободная линия (контакт В8 NOWS-‘No Wait State’) исходной 8-битной шины. При установке этой линии в 0 такты ожидания пропускаются. Использование в качестве NOWS линии исходной шины позволяло разработчикам делать как 16-битные, так и 8-битные «быстрые» платы.

Новый слот содержал 4 новых адресных линии (LA20-LA23) и копии трех младших адресных линий (LA17-LA19). Необходимость в таком дублировании возникла из-за того, что адресные линии ХТ были линиями с задержкой (latched lines), и эти задержки приводили к снижению быстродействия периферийных устройств. Использование дублирующего набора адресных линий позволяло 16-битной карте в начале цикла определить, что к ней обращаются, и послать сигнал о том, что она может осуществлять 16-битный обмен. На самом деле, это ключевой момент в обеспечении обратной совместимости. Если процессор пытается осуществить 16-битный доступ к плате, он сможет это сделать только в том случае, если получит от нее соответствующий отклик IO16. В противном случае чипсет инициирует вместо одного 16-битного цикла два 8-битных. И все бы было хорошо, но адресных линий без задержки всего 7, поэтому платы, использующие диапазон адресов меньший, чем 128Кбайт, не могли определить, находится ли переданный адрес в их диапазоне адресов, и, соответственно, послать отклик IO16. Таким образом, многие платы, в том числе платы EMS, не могли использовать 16-битный обмен. Подробнее о функционировании шины ISA можно прочитать в описании.

Несмотря на отсутствие официального стандарта и технических «изюминок» шина ISA превосходила потребности среднего пользователя образца 1984 года, а «засилье» IBM AT на рынке массовых компьютеров привело к тому, что производители плат расширения и клонов AT приняли ISA за стандарт. Такая популярность шины привела к тому, что слоты ISA до сих пор присутствуют на всех системных платах, и платы ISA до сих производятся. Правда, Microsoft в спецификации PC99 предусматривает отказ от ISA, но, как говорится, до этого нужно еще дожить.

Архитектура ЭВМ

Компоненты ПК

Интерфейсы

Мини блог

Самое читаемое

Системные платы

Шина ISA

Шина ISA (Industrial Standard Architecture — промышленная стандартная архитектура) использовалась в первом компьютере IBM PC, выпущенном в 1981 году, а в 1984 году — в расширенном 16-разрядном варианте в IBM PC/AT. Шина ISA — это основополагающий базис архитектуры персональных компьютеров; она использовалась вплоть до конца 1990-х годов. Кажется странным, что шина с такой “древней” архитектурой использовалась в высокопроизводительных компьютерах, выпускавшихся до конца 1990-х годов, но это объясняется ее надежностью, широкими возможностями и совместимостью. К тому же эта шина до сих пор работает быстрее большинства подключаемых к ней периферийных устройств.

Примечание!

Существует два варианта шины ISA, различающихся количеством разрядов данных: старая 8-разрядная версия и новая 16-разрядная. Старая версия работала на тактовой частоте 4,77 МГц в компьютерах классов PC и XT. Новая версия использовалась в компьютерах класса AT с тактовыми частотами 6 и 8 МГц. Позже было достигнуто соглашение о стандартной максимальной тактовой частоте 8,33 МГц для обеих версий шин, что обеспечило их совместимость. В некоторых системах допускается использование шин при работе с большей частотой, но не все платы адаптеров выдерживают такую скорость. Для передачи данных по шине требуется от двух до восьми тактов. Поэтому максимальная скорость передачи данных по шине ISA составляет 8,33 Мбайт/с:

8,33 МГц × 16 бит : 2 такта = 66,64 Мбит/с (или 8,33 Мбайт/с)

Полоса пропускания 8-разрядной шины вдвое меньше (4,17 Мбайт/с). Однако не забывайте, что это теоретические максимумы — из-за сложного протокола обмена данными реальная пропускная способность шины намного ниже (обычно вдвое). Но даже в этом случае шина ISA работает быстрее, чем большинство подключенных к ней периферийных устройств.

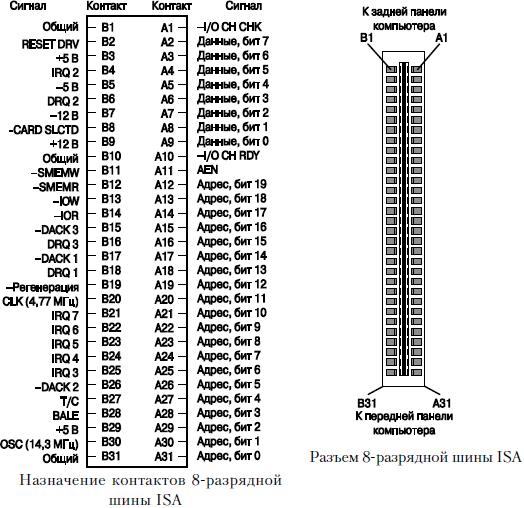

8-разрядная шина ISA

Эта шина использовалась в первом компьютере IBM PC. В новых системах она не применяется, но до сих пор эксплуатируются сотни тысяч компьютеров с такой шиной, в том числе системы на базе процессоров 286 и 386.

В разъем вставляется плата адаптера с 62 контактами. На разъем подаются 8 линий данных и 20 линий адреса, что позволяет адресовать до 1 Мбайт памяти. Назначение и расположение контактов разъема 8-разрядной шины ISA показано на рисунке.

Хотя эта шина очень проста, компания IBM до 1987 года не публиковала ее полного описания и временных диаграмм сигналов на линиях данных и адреса. Поэтому при создании плат адаптеров для первых IBM-совместимых компьютеров разработчикам приходилось самим разбираться в ее работе. По мере распространения IBM-совместимых компьютеров и их превращения в промышленный стандарт процесс разработки существенно упростился.

Плата адаптера для 8-разрядной шины ISA имеет следующие размеры:

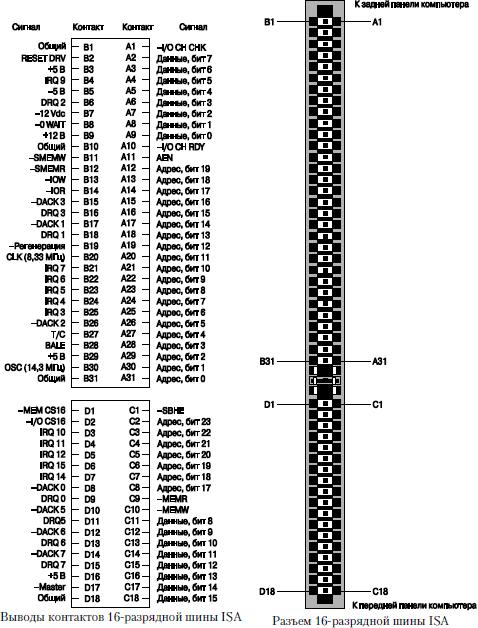

16-разрядная шина ISA

Компания IBM буквально “взорвала” мир ПК, представив в 1984 году модель AT, оснащенную процессором 286. Данный процессор поддерживал 16-разрядную шину данных, что позволяло обеспечить взаимодействие между процессором, системной платой и памятью с использованием 16-разрядных, а не 8-разрядных данных. Хотя процессор и можно было установить на системной плате с 8-разрядной шиной ввода-вывода, все равно обеспечивалось повышенное быстродействие при обмене данными с различными платами, подключаемыми к шине.

Вместо того чтобы создавать новую шину ввода-вывода, IBM решила обеспечить совместимость системы с 8- и 16-разрядными адаптерами, оставив тот же 8-разрядный разъем, но добавив к нему еще один дополнительный. В результате был получен разъем для установки 16-разрядных адаптеров. Впервые представленная в компьютерах PC/AT в августе 1984 года 16-разрядная шина ISA также называлась шиной AT.

Дополнительный разъем в каждом 16-разрядном разъеме расширения добавляет 36 контактов (общее количество контактов для передачи данных при этом увеличивается до 98), необходимых для передачи данных большей разрядности. Кроме того, было изменено назначение двух контактов 8-разрядной части разъема. Однако подобные изменения никак не отразились на работоспособности 8-разрядных плат.

Обычная плата адаптера класса AT имеет следующие размеры:

В компьютерах класса AT могут встретиться платы высотой как 4,8 дюйма, так и 4,2 дюйма (соответствующие старым платам для компьютеров класса PC/XT). Платы с уменьшенной высотой устанавливались в компьютере класса XT модели 286. В данной модели с системной платой, предназначенной для компьютера класса AT, использовался корпус от XT, поэтому высоту плат адаптеров пришлось уменьшить до 4,2 дюйма. После этого большинство производителей стали выпускать только адаптеры с уменьшенной высотой, которые можно установить в любой корпус.

32-разрядная шина ISA

Спустя некоторое время после выпуска 32-разрядного процессора были разработаны первые стандарты на соответствующую шину. Еще до появления первых проектов архитектур МСА и EISA некоторые компании начали разрабатывать собственные конструкции, представляющие собой расширение архитектуры ISA. Хотя их было выпущено сравнительно немного, некоторые из них встречаются даже сейчас.

Дополнительные линии этих шин обычно использовались только при работе с платами расширения памяти и видеоадаптерами, выпускаемыми компаниями, создавшими данный стандарт. Их параметры и разводки разъемов существенно отличаются от стандартных, к тому же их спецификации и схемы контактов не распространялись.

Шина ISA

В основе этого материала книга сотрудника нашей компании Блохнина С.М. по шине ISA, изданная ПК «Сплайн» в 1992 году.

шина AT компьютеров позволяет использовать на внешних платах как 16-разрядные устройства ввода/вывода, так и 16-разрядную память;

цикл доступа к 16-разрядной памяти на внешней плате может быть выполнен без вставки тактов ожидания;

объем непосредственно адресуемой памяти на внешних платах может достигать 16 Мб;

внешняя плата может становиться хозяином (задатчиком) на шине и самостоятельно осуществлять доступ ко всем ресурсам как на шине, так и на материнской плате.

Кроме этого, на материнской плате компьютера имеется ряд устройств, которые не могут быть задатчиками на шине, но тем не менее взаимодействуют с ней. Это следующие устройства:

Архитектура персонального компьютера IBM PC/AT с точки зрения использования шины ISA показана на рисунке.

Центральный процессор по умолчанию является основным владельцем шины, контроллер ПДП и контроллер регенерации памяти могут стать задатчиками на шине, только предварительно запретив работу ЦП. Процесс запрещения работы ЦП состоит в выработке сигнала запроса на ПДП и приема сигнала подтверждения ПДП.

Центральный процессор может быть источником как 16-разрядных операций, так и 32-разрядных. Когда ЦП является 16-разрядным ресурсом, он может выполнять операции как с 16-, так и с 8-разрядными ресурсами на шине. При выполнении ЦП команды, оперирующей с 16-разрядными данными, если ресурс доступа 8- разрядный, то специальными аппаратными средствами на материнской плате в этом случае выполняются два цикла доступа. Если же ЦП является 32-разрядным, то аппаратно на материнской плате компьютера один 32-разрядный цикл работы ЦП с внешним ресурсом должен быть преобразован в два индивидуальных 16-разрядных цикла доступа.

Особенности для внешних плат. Если ЦП является задатчиком на шине, то внешние платы могут функционировать только в режиме памяти или устройства ввода/вывода.

ПРИМЕЧАНИЕ: 8-разрядная память со своей стороны может передавать данные в режиме ПДП только 8-разрядным устройствам ввода/вывода; использование 8-разрядной памяти с 16-разрядными устройствами ввода/вывода не допускается.

ВНИМАНИЕ! Контроллер регенерации памяти не может захватить шину до тех пор, пока контроллер ПДП ей владеет. Это означает, что любой цикл ПДП не должен превышать 15 мкс. В противном случае может произойти потеря информации в микросхемах динамической памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигналы запроса и подтверждения режима ПДП заведены на все внешние платы и эти сигналы вырабатываются обычными ТТЛ выходами, поэтому все внешние платы должны использовать и анализировать различные каналы ПДП. В противном случае возможен конфликт внешних слотов между собой или с устройствами на материнской плате.

Внешние слоты могут быть или памятью прямого доступа или устройством ввода/вывода, когда они взаимодействуют с контроллером ПДП.

Внешние платы могут функционировать в 5 различных режимах: задатчика шины, памяти и устройств ввода/вывода прямого доступа, памяти и устройств ввода/вывода, регенерации памяти или сброса. Платы могут поддерживать любую комбинацию из первых четырех режимов; сигналу сброса должны подчиниться все платы одновременно.

ПРИМЕЧАНИЕ: Программное обеспечение, поддерживающее работу внешней платы в качестве задатчика шины, должно обеспечивать использование каналов ПДП только в режиме каскадирования. В противном случае внешняя плата не сможет осуществить захват шины.

Внешняя плата может работать в режиме ПДП только в том случае, если контроллер ПДП является задатчиком на шине. В режиме прямого доступа к памяти данные всегда передаются между устройством ввода/вывода и памятью на внешней плате. В режиме прямого доступа к устройству ввода/вывода данные передаются между памятью и устройством ввода/вывода на внешней плате. Внешняя плата, отвечающая на шине как 8- или 16-разрядное устройство, должна соответственно использовать 8- или 16- разрядные каналы контроллера ПДП. В табл. 2.2 показано состояние сигналов на шине для режима ПДП.

Внешняя плата может как 16-разрядная память обмениваться в режиме ПДП как с 8-ми разрядными устройствами ввода/вывода, так и с 16-разрядными. Но, если внешняя плата является 8-разрядной памятью, то в режиме ПДП она может обмениваться данными только с 8-разрядными устройствами ввода/вывода. Другая особенность относится к тому случаю, когда контроллер ПДП выполняет запись данных в 8- разрядное устройство вывода на внешней плате из 16-разрядной памяти. Если такая внешняя плата установлена в 16-разрядный слот и может работать в 16-разрядном режиме, она должна для такого случая поддерживать старшую половину шины данных SD в третьем состоянии во избежание столкновения сигналов на шине.

ВНИМАНИЕ! Существуют особенности такого использования внешней платы, если она устанавливается в [8/16] слот, а участвует в обмене данными как 8-разрядная память или УВВ в течении всего цикла доступа. При чтении данных в такую внешнюю плату перестановщик байтов будет переставлять данные между шинами SD или SD для правильного приема данных внешней платой. Внешняя плата при этом должна поддерживать свои выходы SD в третьем состоянии, так как иначе неизбежно столкновение сигналов на шине данных.

ВНИМАНИЕ! Циклы регенерации должны выполняться каждые 15 мкс для перебора всех 256 адресов за 4 мс. Если это условие не выполняется, данные, хранящиеся в динамической памяти, могут быть утеряны.

В данной главе рассматриваются характеристики шины, не зависящие от типа устройства, захватившего шину.

ВНИМАНИЕ! Микросхемы динамической памяти требуют циклов регенерации через каждые 15 мкс. Если циклы регенерации выполняются реже, чем через 15 мкс, то данные в памяти могут быть потеряны.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Несмотря на то, что для выбора адреса УВВ доступны все 16 сигналов адреса, традиционно для адресов УВВ в компьютерах серии IBM PC/XT/AT использовались только первые 10 разрядов адреса. Это означает, что адреса из следующих килобайтных блоков будут декодироваться также как адреса в первом килобайте адресов УВВ. Поэтому для вновь разрабатываемых внешних плат следует использовать «окна» в существующем сейчас распределении адресов стандартных УВВ для компьютеров IBM PC/AT. Для увеличения количества используемых адресов УВВ (при необходимости) можно использовать адресное пространство выбранного окна со сдвигом на 1 Кб или кратное ему значение. Очевидно, что внешняя плата в этом случае должна декодировать более чем 10 линий адреса.

Линии запроса на прерывания непосредственно заведены на контроллеры прерываний типа Intel 8259A. Контроллер прерываний будет реагировать на запрос по такой линии в случае, если сигнал на ней перейдет из низкого уровня в высокий. Шина ISA не имеет линий, подтверждающих прием запроса на прерывание, поэтому запрашивающее прерывание устройство должно само определять по реакции ЦП подтверждение приема своего запроса.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Линии запроса на прерывания заведены на все слоты и обрабатываются контроллером прерывания по нарастающему фронту сигнала. До установки новой внешней платы, если она использует в своей работе контроллер прерываний, следует определить, есть ли свободная линия запроса на прерывание и именно ее использовать для новой внешней платы. При не соблюдении этого условия возможно возникновение конфликтных ситуаций на шине.

ПК «Сплайн-Технолоджис»

Профессиональный подход.

Разумность решений.

Новости

Шина ISA

шина AT компьютеров позволяет использовать на внешних платах как 16-разрядные устройства ввода/вывода, так и 16-разрядную память;

цикл доступа к 16-разрядной памяти на внешней плате может быть выполнен без вставки тактов ожидания;

объем непосредственно адресуемой памяти на внешних платах может достигать 16 Мб;

внешняя плата может становиться хозяином (задатчиком) на шине и самостоятельно осуществлять доступ ко всем ресурсам как на шине, так и на материнской плате.

Кроме этого, на материнской плате компьютера имеется ряд устройств, которые не могут быть задатчиками на шине, но тем не менее взаимодействуют с ней. Это следующие устройства:

Архитектура персонального компьютера IBM PC/AT с точки зрения использования шины ISA показана на рисунке.

Центральный процессор по умолчанию является основным владельцем шины, контроллер ПДП и контроллер регенерации памяти могут стать задатчиками на шине, только предварительно запретив работу ЦП. Процесс запрещения работы ЦП состоит в выработке сигнала запроса на ПДП и приема сигнала подтверждения ПДП.

Центральный процессор может быть источником как 16-разрядных операций, так и 32-разрядных. Когда ЦП является 16-разрядным ресурсом, он может выполнять операции как с 16-, так и с 8-разрядными ресурсами на шине. При выполнении ЦП команды, оперирующей с 16-разрядными данными, если ресурс доступа 8- разрядный, то специальными аппаратными средствами на материнской плате в этом случае выполняются два цикла доступа. Если же ЦП является 32-разрядным, то аппаратно на материнской плате компьютера один 32-разрядный цикл работы ЦП с внешним ресурсом должен быть преобразован в два индивидуальных 16-разрядных цикла доступа.

Особенности для внешних плат. Если ЦП является задатчиком на шине, то внешние платы могут функционировать только в режиме памяти или устройства ввода/вывода.

ПРИМЕЧАНИЕ: 8-разрядная память со своей стороны может передавать данные в режиме ПДП только 8-разрядным устройствам ввода/вывода; использование 8-разрядной памяти с 16-разрядными устройствами ввода/вывода не допускается.

ВНИМАНИЕ! Контроллер регенерации памяти не может захватить шину до тех пор, пока контроллер ПДП ей владеет. Это означает, что любой цикл ПДП не должен превышать 15 мкс. В противном случае может произойти потеря информации в микросхемах динамической памяти.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Сигналы запроса и подтверждения режима ПДП заведены на все внешние платы и эти сигналы вырабатываются обычными ТТЛ выходами, поэтому все внешние платы должны использовать и анализировать различные каналы ПДП. В противном случае возможен конфликт внешних слотов между собой или с устройствами на материнской плате.

Внешние слоты могут быть или памятью прямого доступа или устройством ввода/вывода, когда они взаимодействуют с контроллером ПДП.

Внешние платы могут функционировать в 5 различных режимах: задатчика шины, памяти и устройств ввода/вывода прямого доступа, памяти и устройств ввода/вывода, регенерации памяти или сброса. Платы могут поддерживать любую комбинацию из первых четырех режимов; сигналу сброса должны подчиниться все платы одновременно.

ПРИМЕЧАНИЕ: Программное обеспечение, поддерживающее работу внешней платы в качестве задатчика шины, должно обеспечивать использование каналов ПДП только в режиме каскадирования. В противном случае внешняя плата не сможет осуществить захват шины.

Внешняя плата может работать в режиме ПДП только в том случае, если контроллер ПДП является задатчиком на шине. В режиме прямого доступа к памяти данные всегда передаются между устройством ввода/вывода и памятью на внешней плате. В режиме прямого доступа к устройству ввода/вывода данные передаются между памятью и устройством ввода/вывода на внешней плате. Внешняя плата, отвечающая на шине как 8- или 16-разрядное устройство, должна соответственно использовать 8- или 16- разрядные каналы контроллера ПДП. В табл. 2.2 показано состояние сигналов на шине для режима ПДП.

Внешняя плата может как 16-разрядная память обмениваться в режиме ПДП как с 8-ми разрядными устройствами ввода/вывода, так и с 16-разрядными. Но, если внешняя плата является 8-разрядной памятью, то в режиме ПДП она может обмениваться данными только с 8-разрядными устройствами ввода/вывода. Другая особенность относится к тому случаю, когда контроллер ПДП выполняет запись данных в 8- разрядное устройство вывода на внешней плате из 16-разрядной памяти. Если такая внешняя плата установлена в 16-разрядный слот и может работать в 16-разрядном режиме, она должна для такого случая поддерживать старшую половину шины данных SD в третьем состоянии во избежание столкновения сигналов на шине.

ВНИМАНИЕ! Существуют особенности такого использования внешней платы, если она устанавливается в [8/16] слот, а участвует в обмене данными как 8-разрядная память или УВВ в течении всего цикла доступа. При чтении данных в такую внешнюю плату перестановщик байтов будет переставлять данные между шинами SD или SD для правильного приема данных внешней платой. Внешняя плата при этом должна поддерживать свои выходы SD в третьем состоянии, так как иначе неизбежно столкновение сигналов на шине данных.

ВНИМАНИЕ! Циклы регенерации должны выполняться каждые 15 мкс для перебора всех 256 адресов за 4 мс. Если это условие не выполняется, данные, хранящиеся в динамической памяти, могут быть утеряны.

В данной главе рассматриваются характеристики шины, не зависящие от типа устройства, захватившего шину.

ВНИМАНИЕ! Микросхемы динамической памяти требуют циклов регенерации через каждые 15 мкс. Если циклы регенерации выполняются реже, чем через 15 мкс, то данные в памяти могут быть потеряны.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Несмотря на то, что для выбора адреса УВВ доступны все 16 сигналов адреса, традиционно для адресов УВВ в компьютерах серии IBM PC/XT/AT использовались только первые 10 разрядов адреса. Это означает, что адреса из следующих килобайтных блоков будут декодироваться также как адреса в первом килобайте адресов УВВ. Поэтому для вновь разрабатываемых внешних плат следует использовать «окна» в существующем сейчас распределении адресов стандартных УВВ для компьютеров IBM PC/AT. Для увеличения количества используемых адресов УВВ (при необходимости) можно использовать адресное пространство выбранного окна со сдвигом на 1 Кб или кратное ему значение. Очевидно, что внешняя плата в этом случае должна декодировать более чем 10 линий адреса.

Линии запроса на прерывания непосредственно заведены на контроллеры прерываний типа Intel 8259A. Контроллер прерываний будет реагировать на запрос по такой линии в случае, если сигнал на ней перейдет из низкого уровня в высокий. Шина ISA не имеет линий, подтверждающих прием запроса на прерывание, поэтому запрашивающее прерывание устройство должно само определять по реакции ЦП подтверждение приема своего запроса.

ОСОБЕННОСТИ ДЛЯ ВНЕШНИХ ПЛАТ

Линии запроса на прерывания заведены на все слоты и обрабатываются контроллером прерывания по нарастающему фронту сигнала. До установки новой внешней платы, если она использует в своей работе контроллер прерываний, следует определить, есть ли свободная линия запроса на прерывание и именно ее использовать для новой внешней платы. При не соблюдении этого условия возможно возникновение конфликтных ситуаций на шине.