Ацп для шины i2c

Ацп для шины i2c

Анонс:

Поставим задачу.

Имеется двуполярный сигнал от источника с высоким внутренним сопротивлением. Необходимо построить схематехнику так, чтобы ни одного подстроечного сопротивления, ни одной калибровки бы не требовалось. Таким источником, например, может быть pH электрод с внутренним сопротивлением доли GΩ и разнополярным сигналом в диапазоне ±250 мВ. (см. http://keklab.ru/articles/3-2010-10-28-21-52-23/18-phmeter.html ).

Задача не решается «в лоб». Внутренний усилитель АЦП, как правило, имеет малый импеданс. Значит надо усилитель на вход по технологии CMOS. Это во-первых. Далее раз усилитель, то чем его питать? Двуполярное питание? Не хотелось бы… А как же ±250 мВ на входе? Это означает создание смещения, а это означает зависимость от точности питания, от точности сопротивлений, организующих смещение, даже при использовании источников опорного напряжения. Вот калибровки и потянутся… Это во-вторых.

Решение определилось в создании искусственной средней точки. Проведя поиск, нашлась даже специальная микросхема TLE2425, которая минимизирует колебания искусственной средней точки. А эти колебания возможны, когда токи потребления отдельных узлов «гуляют». Вот здесь об этом:

Но в представленном решении оказалось все проще. Пусть себе гуляет. Я имею ввиду не кошку, а искусственную среднюю точку. Она организована может быть совершенно не симметрично относительно питания 3.3V, совершенно не точными сопротивлениями. Главное, чтобы суммарный ток через Rg1 и Rg2 был бы существенно выше потребления усилителя и АЦП, они единственные потребители, которые зависят от средней точки. Почему не важна стабильность? Да, потому, что средняя точка заведена на “-” внутреннего усилителя АЦП и входной сигнал тоже на неё опирается. Вот если бы минус этого АЦП сидел бы на земле, тогда точность средней точки относительно земли имела бы важное значение.

Теперь про усилитель.

А он ничего и не усиливает, а только повторяет и организует преобразование высокого импеданса в потребный для АЦП. Никаких сопротивлений, никаких подстроечников… красота! Если только кому-то потребуется, чтоб он усиливал сигнал, пиши пропало… Точные сопротивления и калибровки вам обеспечены. Хотя есть решение и здесь. Если вместо OPA335 поставить INA333, то можно и усиливать. Но! Точность усиления будет определяться точностью RG (см. pdf). OPA335 имеет один параметр, который позволяет «забыть» про смещения входных токов и напряжений: ZERO DRIFT: 0.05μV/°C (max).

Теперь про АЦП.

Хоть он и 18-ти разрядный, используем только 16. Это будет сказываться на скорости преобразования дельта-сигма. Вот здесь мы можем усиливать сигнал, не заботясь о точности, всё внутри. 1-2-4-8 – возможные варианты параметра усиления PGA. Правда надо отметить, что собственный входной импеданс АЦП зависит от усиления и составляет R=2.25/PGA (MΩ).

В дифференциальном режиме АЦП выдает код, который можно преобразовать в двуполярное значение, мы же этого хотели. В pdf очень «туго» все написано, поэтому, чтобы люди не мучились вот кусок формулы на СИ:

ADC_MCP3421 = (B1

if (ADC_MCP3421

SignADC_MCP3421 = ADC_MCP3421;

else

Всем хорош данный АЦП, кроме одного нюанса. Если необходимо иметь несколько таких АЦП, каскадно соединенных по I2C, то адрес выбирается не ручками, а отслеживается при заказе на фирме, где вы покупаете. Для меня это было новостью.

Что касается I2C, то моя практика показала достаточную надежность данного компактного интерфейса при возможности каскадного внутриблочного соединения. Да, и еще, при правильной настройки всех регистров оного. Это будет отражено в материалах для ссылок.

Теперь про микроконтроллер. А точнее про некоторые программные средства, позволяющие уменьшить наводимую помеху.

При большом входном импедансе помехи будут вас донимать. Импульсные и пятидесятигерцовые. Борьба с импульсными помехами описана в этой сказке. А от прочих, помимо экранировки и заземления, помогает метод, который давно используется

Конечно все это справедливо для «неспешных» измерений, где истинное значение необходимо не чаще, чем раз в секунду или в две.

В микроконтроллере организуется системное прерывание. Если есть кварц, то организуется интервал проведения измерения. В данной схеме 80 мс. Буфер adcdata за две секунды накапливает 25 значений. Затем процедура qsort(), которая входит в стандартный набор AVR-Studio, сортирует этот массив по возрастанию. Значение буфера adcdata[13] – отфильтрованное. В этом заключается медианная (серединная) фильтрация. Чем это лучше просто среднего значения?

Возьмем короткий буфер array[5] = <1002, 1010, 999, 1001, 1100>, в который записываем значения АЦП SignADC_MCP3421. Такой он получился после реальных измерений, на которые действует импульсная помеха. Последнее значение резко отличается от остальных из-за этого. Среднее будет = 1022;

После сортировки массив будет таков: array[5] = <999, 1001, 1002, 1010, 1100>;

Медианная фильтрация после сортировки выдаст значение array[2] = 1002. Это значение более точное и не учитывает помеховый выброс. Конечно, можно из необработанного массива выбирать максимальное и минимальное значение и не учитывать их при подсчете среднего. А если таких максимумов будет несколько? По сути медианная фильтрация это и делает.

Важным моментом является период измерений. Контроллер ничего не знает о фазе пятидестигерцовой помехи, она не синхронизирована с моментом начала измерения.

На практике на вход данной схемы было подано 200 мВ синусоидального сигнала с частотой 50 Гц. (см. осциллограммы). Эта синусоида имитировала помеху, наведенную на постоянный сигнал в 100 мВ. Моменты измерения показаны ниже импульсами с периодом в 80 мс. Как видно в двух случаях (осц.1 и осц.2) моменты измерения приходятся на разные фазы синусоиды.

Медианная фильтрация выдавала значение около 100мВ. Соотношение сигнал/шум при этом 100%. Реальный разброс измерения за несколько сеансов составил диапазон от 97.90625мВ до 100.65625мВ. Ошибка составила 2.75%. Ошибка большая, но надо иметь в виду, что реальное соотношение сигнал/шум будет на порядок меньше.

В материалах представлен проект в AVR-Studio ver 4.18 Build 716 для Atmega16A. Он без комментариев, как есть. В нем реализуется алгоритм измерения и метод медианой фильтрации. Так же представлены процедуры для простой организации интерфейса I2C. На практике этот интерфейс так же подвержен помехам. Чтобы это не приводило к «зависанию» организованы некие действия в процедуре void twi_stop(void). Эти материалы можно использовать в организации связи многочисленных Slave-Unit, которые охватывают широкий спектр приборов:

В заключении.

Данная схема легла в основу реального проекта. Она была дополнена схемотехникой гальванической развязки на:

Ацп для шины i2c

Так же как и в прошлый раз, упор будет делаться на «чистом» программировании на Си и Ассемблере без использования сторонних библиотек. В качестве компилятора используется open-source SDCC версии 3.7. Справедливости ради замечу, что я ввёл макросы для прямого доступа к битовым инструкциям, что бы хоть как-то оптимизировать код.

Скачать полные исходники со сборочными файлам и скомпилированными прошивками, можно по ссылке в конце статьи.

В статье используются формулы в формате MathML который поддерживается браузером Firefox, для браузеров Chrome и Opera потребуется установить одноимённое расширение MathML.

1. UART1 передатчик со скоростью 921600 baud

Документация на чип STM8S103f3 обещает нам скорость UART протокола

1 Mbit/sec при частоте fMASTER=16МГц. От себя замечу, что заявленная скорость доступна и без внешнего кварца или генератора.

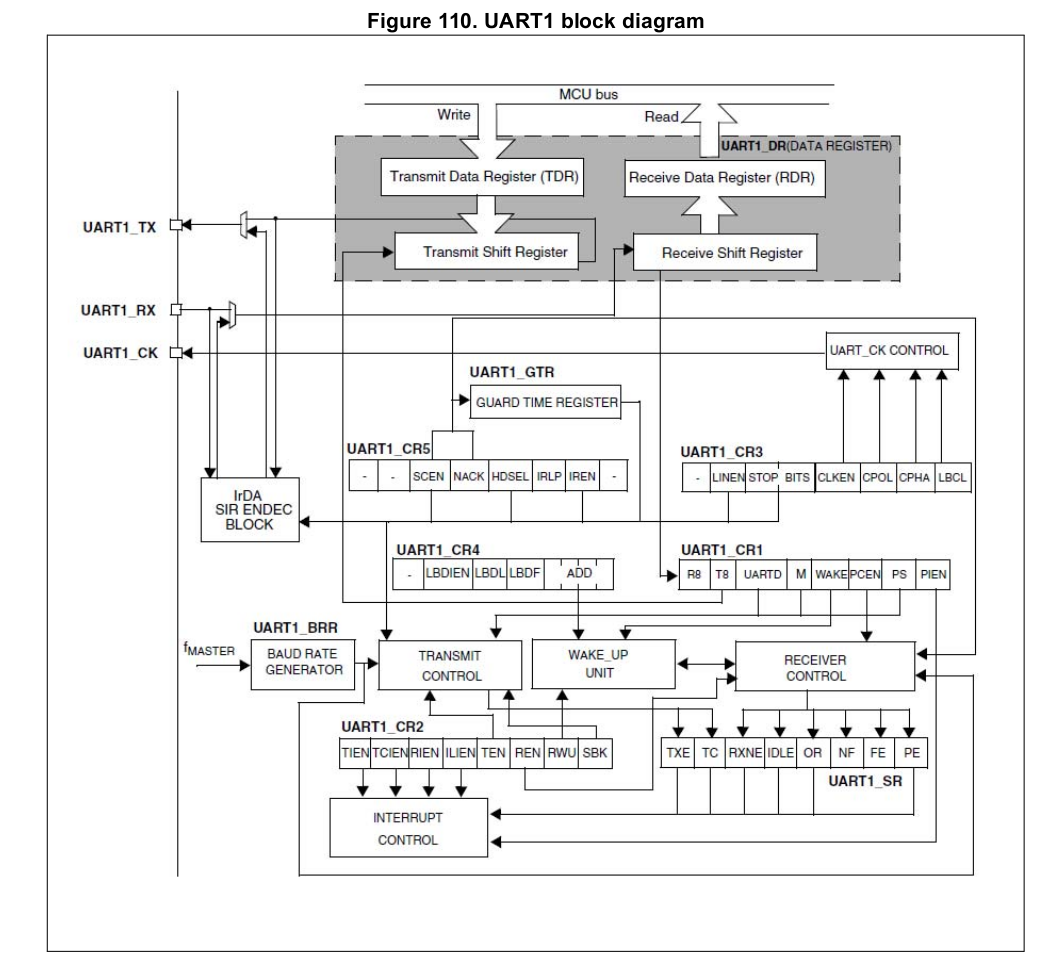

Блок-схема модуля UART1 представлена на картинке ниже:

UART1 включает в себя один флаговый регистр UART1_SR1 и пять конфигурационных: UART1_CR1, UART1_CR2, UART1_CR3, UART1_CR4, UART1_CR5. Кроме регистра данных UART1_DR имеются также пара регистров для указания битрейта: UART1_BRR1 и UART1_BRR2, регистр предделителя: UART1_PSCR, и защитный регистр UART1_GTR для Smartcard режима.

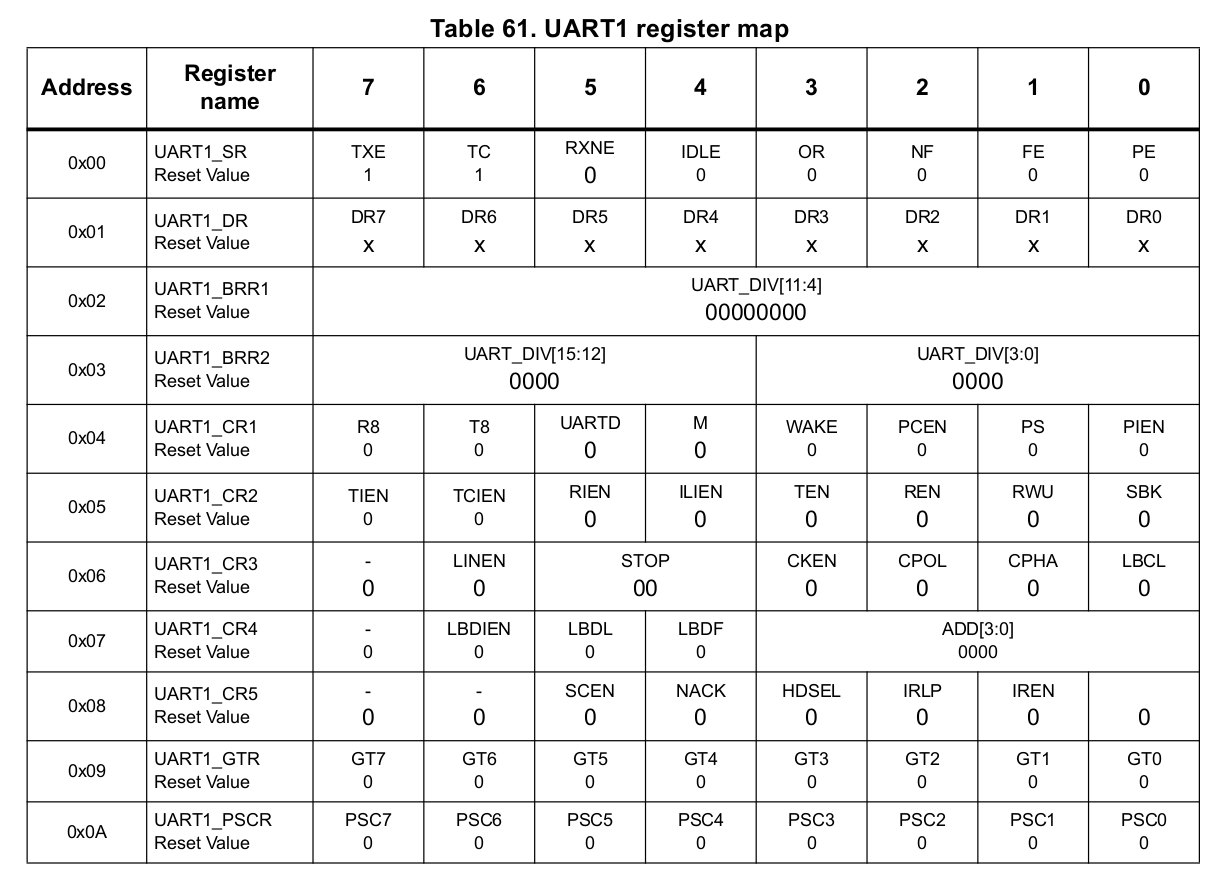

Общая карта регистров с предустановленными значениями показана в следующей табличке:

Значения регистров я рассматривал в статье STM8S+SDCC+SPL: использование модуля UART1 на примере функции printf(). Для того чтобы сконфигурировать и запустить UART1 передатчик нужно иметь в виду всего три флага.

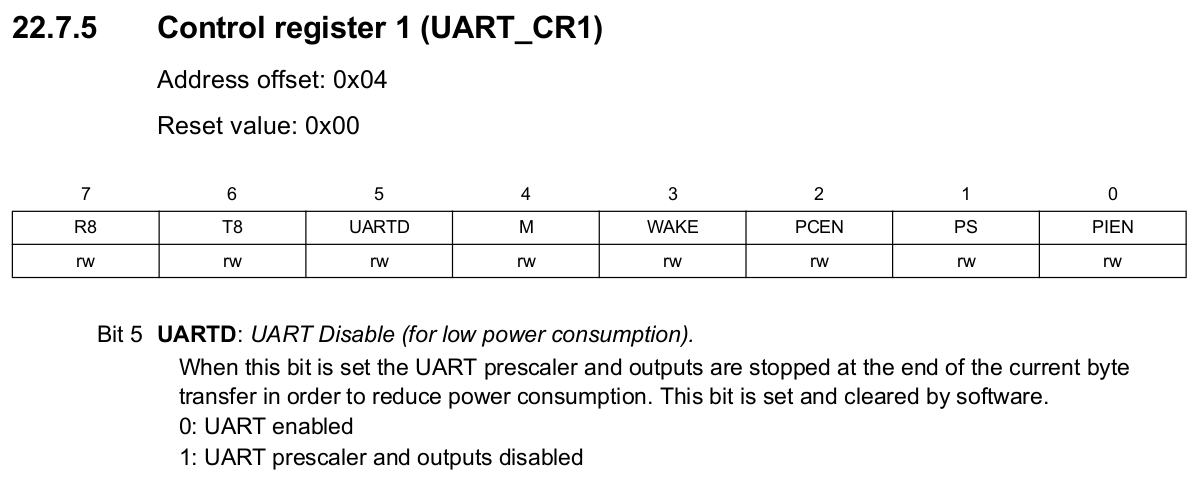

В UART1_CR1 это флаг UARTD который включает и выключает модуль UART1. Обращаю внимание, что в сброшенном состоянии флага, модуль UART1 включён:

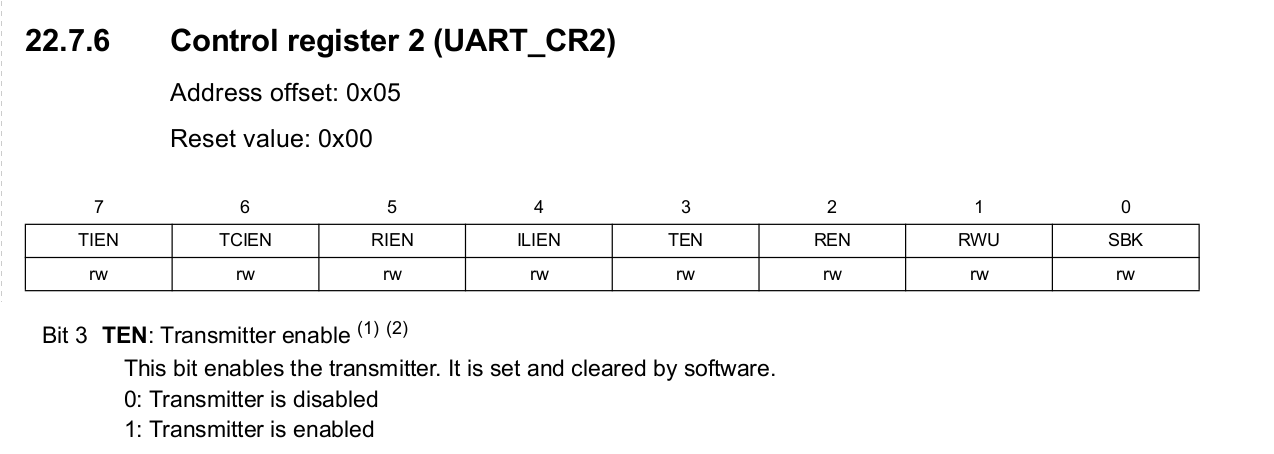

В регистре UART1_CR2 нас будет интересовать флаг TEN который включает передатчик:

И во флаговом регистре UART1_SR1 нас будет интересовать бит TXE, который устанавливается в момент передачи содержимого UART1_DR в сдвиговый регистр. Т.е. в момент, когда UART1_DR освободится. Очищается этот флаг путём записи в UART1_DR.

В качестве шаблона проекта я взял пример из предыдущей статьи: Передача параметров из Си в ассемблерную функцию

В результате у меня получился такой исходник:

Макросы: регистр_bset(), регистр_bres(), регистр_bcpl() определены в заголовочном файле stm8s103f.h. Они заменяются ассеблерными инструкциями:

Функцией printf() я в этот раз не пользовался, они слишком тяжёлая. Поэтому ее пришлось заменить несколькими самописными функциями для передачи данных через UART:

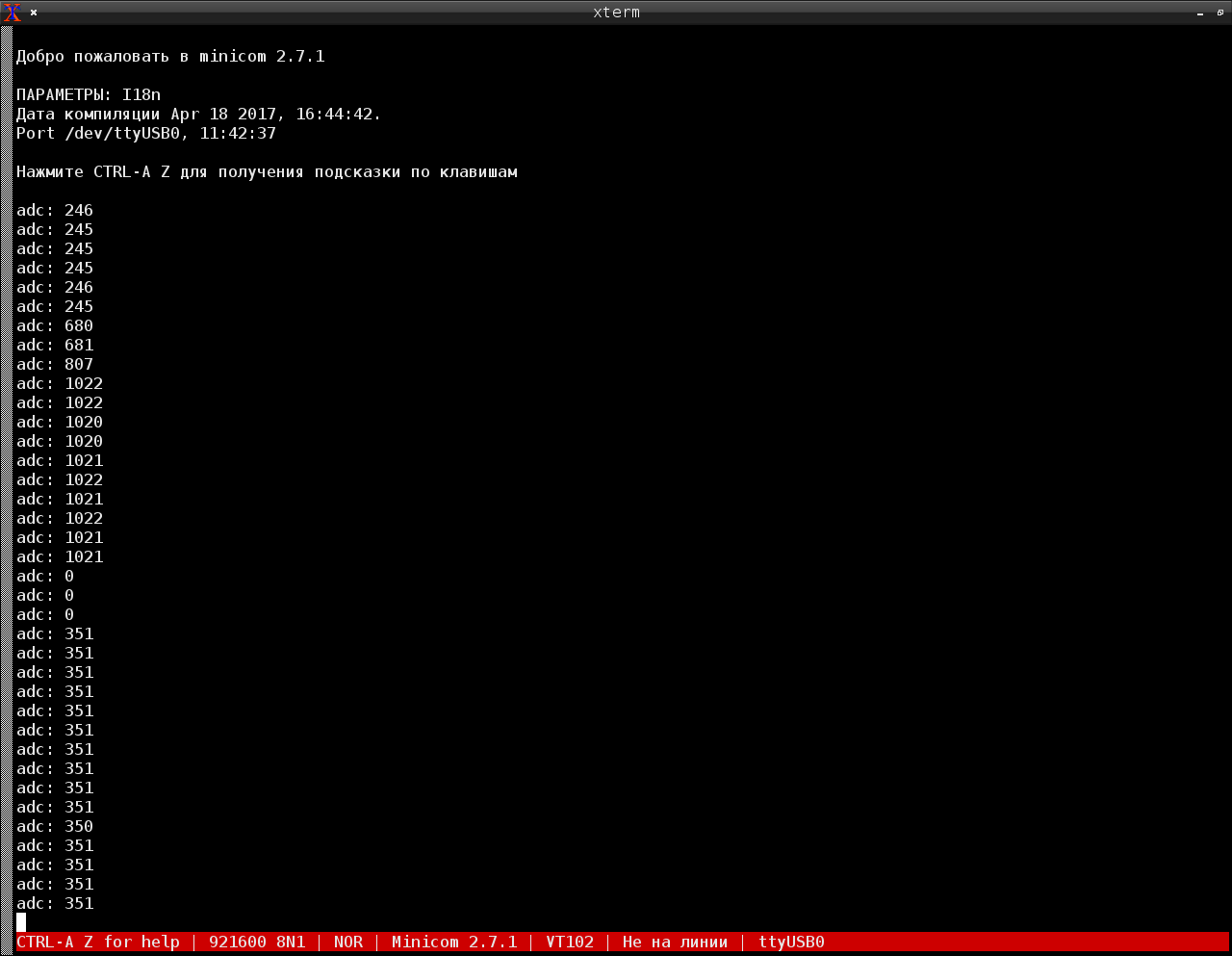

Прошивка весит 284 байта. Посмотреть вывод в можно в любой терминальной программе, например в Linux c помощью minicom:

или через Arduino IDE, вызвав монитор последовательного порта.

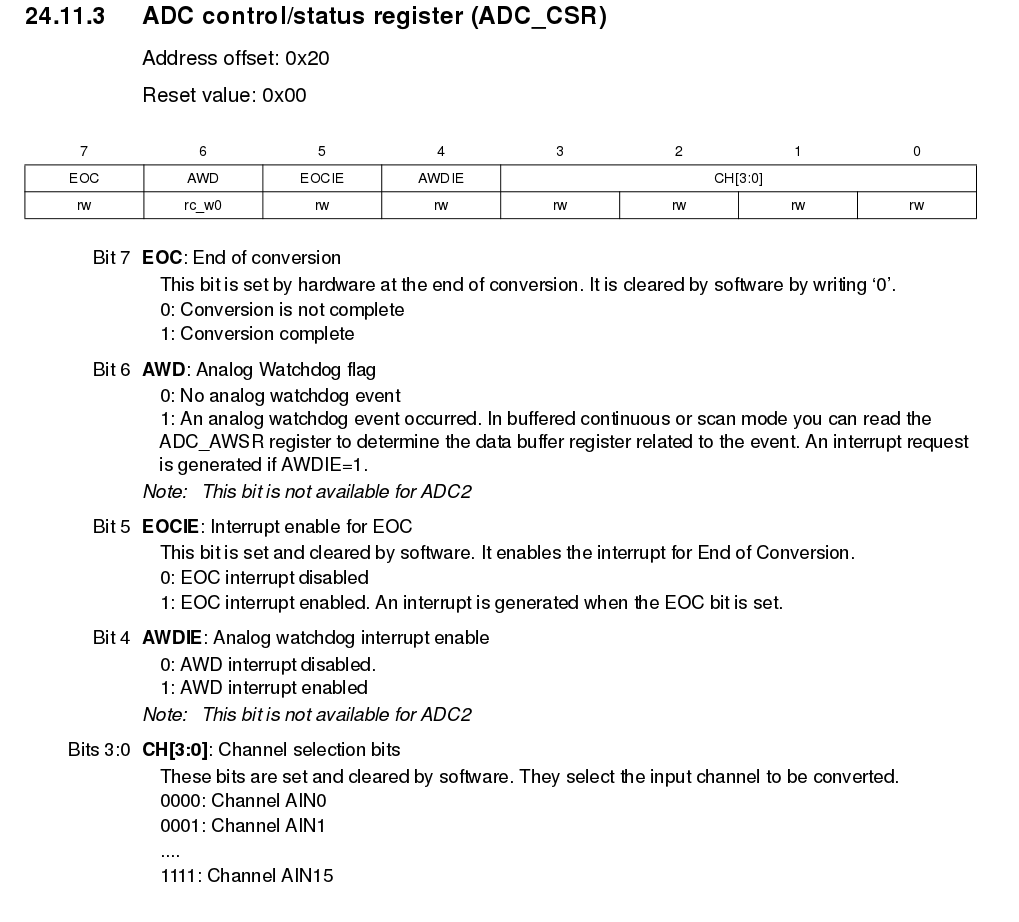

2. АЦП в режиме однократного замера

В STM8S имеется 10-битный АЦП, и так как сам микроконтроллер является 8-битным, имеются варианты выравнивания результата, для получения однобайтного 8-битного числа или двухбайтного 10-битного. Варианты выравнивания представлены на картинке ниже:

Нетрудно догадаться, что выравнивание по левому краю удобно для получения 8-битного значения АЦП, а выравнивание по правому удобно для получения 10-битного значения.

Если говорить о режиме однократного замера, то кроме вышеупомянутой регистровой пары ADC_DR, нас будут интересовать ещё несколько РВВ:

Здесь через SPSEL[2:0] устанавливается частота дискретизации АПЦ. Через бит CONT устанавливается или сбрасывается непрерывный режим работы АЦП. ADON включает или выключает АЦП.

Также не стоит забывать про регистры отключающие триггеры Шмитта:

Здесь каждый бит соответствует своему каналу. Отключение триггера делает невозможным использование соответствующего пина в качестве пина цифрового ввода-вывода, а оставление его включённым значительно снижает точность измерения АЦП. Триггер отключается записью единицы.

Вариант программы для получения 8-значения с АЦП и вывода его через UART у меня получился таким:

Я подключил на пин РС3 потенциометр и пару раз покрутив ручкой получил такой результат:

Как видно, работает вполне нормально, не шумит, однако в программе есть «подводный камень». Если закомментировать строку: AWU_CSR = 0x10, пересобрать и перезалить прошивку, то она работать не будет. Микроконтроллер не будет выходить из режима сна после инструкции wfi. Попытка заменить инструкцию wfi на цикл ожидания установки флага EOC не поможет. При этом если закомментировать на этот раз инструкцию wfi, то программа вроде как работает. Какая взаимосвязь между AWU и АЦП, я честное слово не знаю. Возможно где-то каким-то образом задевается аналоговый watchdog. Могу только уверенно сказать что дело не в микроконтроллере. Аналогичная программа на ассемблере на том же микроконтроллере работает без всякого AWU, но вот при переносе алгоритма на Си, возникла такая проблема. Так что я предполагаю что дело в компиляторе SDCC, что весьма печально.

Вариант программы для 10-битного АЦП, представлен ниже:

Результат работы с тем же потенциометром:

На мой взгляд, для 10-битного АЦП это вполне достойный результат. Шумит только последний бит, да и то, слегка.

3. I 2 C в режиме мастера, на примере RTC DS1307/DS3231. Инициализация

Чтобы, составить полное мнение о возможностях I 2 C модуля, нужно будет ознакомиться с его конфигурационными регистрами. Мне лично модуль понравился, это мощная и гибкая штука. Сейчас мне хотелось бы рассмотреть самый простой режим его работы: режим мастера на стандартной скорости 100кГц и 7-битным I 2 C адресом, без использования прерываний (работа в режиме опроса). В качестве слейва я выбрал RTC DS3231, с которым наверное уже все знакомы.

Порядок работы с I 2 C я бы разделил на инициализацию и рабочий цикл. Думаю, что сначала имеет смысл рассмотреть регистры которые отвечают за инициализацию.

В данном случае, инициализация занимает 8 строчек кода и затрагивает 5 регистров:

Инициализация I 2 C модуля состоит из задания скорости работы и переключения в нужный режим: стандартная скорость шины, 7-битный адрес. Переключение в режим мастера и обратно в слейв происходит автоматически, после команд START и STOP.

где значением CCR является:

P e r i o d I 2 C = 2 * C C R * T M A S T E R

C C R = P e r i o d I 2 C 2 * T M A S T E R

К примеру для частоты I2C шины =100 кГц, и частоты fMASTER = 16 МГц, имеем значение CCR=80:

Проще конечно вычислять CCR как отношение частоты fMASTER к частоте I 2 C шины:

C C R = f M A S T E R 2 * f I 2 C

Здесь сейчас интересен только флаг PE, который включает/выключает работу модуля. Вся конфигурация должна происходить при сброшенном PE флаге!

4. I 2 C в режиме мастера, на примере RTC DS1307/DS3231. Функция передачи адреса и данных

Функция передачи I 2 C адреса и записи одного числа у меня получилась такая (параметры функции читаются из стека):

Это наверно самый простейший случай, здесь не анализируется ответ слейва, всегда предполагается что он на линии и отвечает ACK’ом.

Сначала посылается сигнал START, затем адрес устройства, затем один байт данных. После чего посылается СТОП и сброс линии. Функция годится для проверки I 2 C модуля. Три цикла обеспечивают гарантированное зависание микроконтроллера, если у вас что-то работает не так.

Важным моментом является то, что для сброса флагов состояния нужно целиком читать регистры, а не пытаться их сбросить битовой операцией.

Флаг STOP. Установка его посылает на линию соответствующий сигнал, после чего I 2 C модуль переводится в режим слейва.

Установка флага SWRST сбрасывает, отпускает линию.

Здесь, флаг SB устанавливается при сигнале START на линии. Флаг очищается программно чтением регистра I2C_SR1. Флаг очищается аппаратно при отключении модуля (PE=0).

Флаг ADDR устанавливается при передаче I 2 C адреса, включая получение отклика ACK. Флаг ADDR НЕ устанавливается при неполучении отклика ACK от слейва! Флаг сбрасывается чтением регистра I2C_SR1 с последующим чтением I2C_SR3. Флаг очищается аппаратно при отключении модуля (PE=0).

5. I 2 C в режиме мастера, на примере RTC DS1307/DS3231. Функция чтения данных

Мощной возможностью STM8 является то, что данные со слейва можно читать порциями по одному, двум, трём байтам или каким-то массивом. Часто при работе по I2C требуется прочитать лишь один или два байта устройства и здесь мы имеем возможность использовать упрощённый алгоритм чтения без циклов.

Отличительной чертой, модуля I 2 C является то, что сигналы ACK, NACK, STOP передаются «пакетом» вместе с читаемым байтом, и они должны быть сконфигурированы ДО(!) чтения этого байта из регистра DR.

Т.к. сессию чтения мастер завершает передачей сигналов NACK и STOP, порядком выставления флагов для формирования этих сигналов и отличаются алгоритмы с завершением сессии чтении в один, два или три байта.

Завершение сессии в один байт, мне показался наиболее универсальным. С его помощью можно читать как один байт, так и массив байтов. Функция чтения массива из семи байт представлена ниже:

Здесь адрес устройства и указатель на массив передаются через стек.

Если из функции убрать цикл чтения шести байт, останется функция чтения одного байта. Как видно, установка флага STOP и сброс флага ACK происходит до чтения последнего байта из регистра DR.

Порядок чтения одного байта в документации представлен следующей диаграммой:

Один, два или три байта можно читать без использования циклов. Например чтобы прочитать текущее время из DS3231 нужно прочитать три байта. Тогда функция чтения будет выглядеть так:

Полная Си-часть программы чтения данных с DS3231:

Хочу обратить внимание, что светодиод для индикации рабочего цикла был перенесён с PB5 на PC3, т.к. пин PB5 занят I 2 C линией.

Текст функций init_i2c() и read_i2c() был представлен выше.

Результат работы в окне программы minicom:

Передача данных. Протокол I2C.

Микроконтроллер на рисунке это ведущий элемент (Master1) им может быть процессор. На рисунке представлено 3 ведомых перефириных элемента Slave В качестве Slave могут быть память, ЦАП, АЦП и пр. К шине может быть подключено до 127 устройств.

Состояние СТАРТ и СТОП

Процедура обмена начинается с того, что ведущий формирует состояние СТАРТ: генерирует переход сигнала линии SDA из ВЫСОКОГО состояния в НИЗКОЕ при ВЫСОКОМ уровне на линии SCL. Этот переход воспринимается всеми устройствами, подключенными к шине, как признак начала процедуры обмена. Генерация синхросигнала — это всегда обязанность ведущего; каждый ведущий генерирует свой собственный сигнал синхронизации при пересылке данных по шине. Процедура обмена завершается тем, что ведущий формирует состояние СТОП — переход состояния линии SDA из низкого состояния в ВЫСОКОЕ при ВЫСОКОМ состоянии линии SCL. Состояния СТАРТ и СТОП всегда вырабатываются ведущим.

Считается, что шина занята после фиксации состояния СТАРТ. Шина считается освободившейся через некоторое время после фиксации состояния СТОП. При передаче посылок по шине I²C каждый ведущий генерирует свой синхросигнал на линии SCL. После формирования состояния СТАРТ ведущий опускает состояние линии SCL в НИЗКОЕ состояние и выставляет на линию SDA старший бит первого байта сообщения. Количество байт в сообщении не ограничено. Спецификация шины I²C разрешает изменения на линии SDA только при НИЗКОМ уровне сигнала на линии SCL. Данные действительны и должны оставаться стабильными только во время ВЫСОКОГО состояния синхроимпульса. Для подтверждения приёма байта от ведущего-передатчика ведомым-приёмником в спецификации протокола обмена по шине I²C вводится специальный бит подтверждения, выставляемый на шину SDA после приёма 8 бита данных.

Подтверждение

Таким образом передача 8 бит данных от передатчика к приёмнику завершаются дополнительным циклом (формированием 9-го тактового импульса линии SCL), при котором приёмник выставляет низкий уровень сигнала на линии SDA, как признак успешного приёма байта.

Подтверждение при передаче данных обязательно, кроме случаев окончания передачи ведомой стороной. Соответствующий импульс синхронизации генерируется ведущим. Передатчик отпускает (переводит в ВЫСОКОЕ состояние) линию SDA на время синхроимпульса подтверждения. Приёмник должен удерживать линию SDA в течение ВЫСОКОГО состояния синхроимпульса подтверждения в стабильном НИЗКОМ состоянии.

В том случае, когда ведомый-приёмник не может подтвердить свой адрес (например, когда он выполняет в данный момент какие-либо функции реального времени), линия данных должна быть оставлена в ВЫСОКОМ состоянии. После этого ведущий может выдать состояние СТОП для прерывания пересылки данных. Если в пересылке участвует ведущий-приёмник, то он должен сообщить об окончании передачи ведомому-передатчику путём неподтверждения последнего байта. Ведомый-передатчик должен освободить линию данных для того, чтобы позволить ведущему выдать состояние СТОП или повторить состояние СТАРТ.

Синхронизация

Синхронизация выполняется с использованием подключения к линии SCL по правилу монтажного И. Это означает, что ведущий не имеет монопольного права на управление переходом линии SCL из НИЗКОГО состояния в ВЫСОКОЕ. В том случае, когда ведомому необходимо дополнительное время на обработку принятого бита, он имеет возможность удерживать линию SCL в низком состоянии до момента готовности к приёму следующего бита. Таким образом, линия SCL будет находиться в НИЗКОМ состоянии на протяжении самого длинного НИЗКОГО периода синхросигналов.

Устройства с более коротким НИЗКИМ периодом будут входить в состояние ожидания на время, пока не кончится длинный период. Когда у всех задействованных устройств кончится НИЗКИЙ период синхросигнала, линия SCL перейдет в ВЫСОКОЕ состояние. Все устройства начнут проходить ВЫСОКИЙ период своих синхросигналов. Первое устройство, у которого кончится этот период, снова установит линию SCL в НИЗКОЕ состояние. Таким образом, НИЗКИЙ период синхролинии SCL определяется наидлиннейшим периодом синхронизации из всех задействованных устройств, а ВЫСОКИЙ период определяется самым коротким периодом синхронизации устройств.

Механизм синхронизации может быть использован приёмниками как средство управления пересылкой данных на байтовом и битовом уровнях.

На уровне байта, если устройство может принимать байты данных с большой скоростью, но требует определенное время для сохранения принятого байта или подготовки к приёму следующего, то оно может удерживать линию SCL в НИЗКОМ состоянии после приёма и подтверждения байта, переводя таким образом передатчик в состояние ожидания.

На уровне битов устройство, такое, как микроконтроллер без встроенных аппаратных цепей I²C или с ограниченными цепями, может замедлить частоту синхроимпульсов путём продления их НИЗКОГО периода. Таким образом скорость передачи любого ведущего адаптируется к скорости медленного устройства.

Адресация в шине I²C

Каждое устройство, подключённое к шине, может быть программно адресовано по уникальному адресу. Для выбора приёмника сообщения ведущий использует уникальную адресную компоненту в формате посылки. При использовании однотипных устройств ИС часто имеют дополнительный селектор адреса, который может быть реализован как в виде дополнительных цифровых входов селектора адреса, так и в виде аналогового входа.

При этом адреса таких однотипных устройств оказываются разнесены в адресном пространстве устройств, подключенных к шине.

В обычном режиме используется 7-битная адресация.

Процедура адресации на шине I²C заключается в том, что первый байт после сигнала СТАРТ определяет, какой ведомый адресуется ведущим для проведения цикла обмена. Исключение составляет адрес «Общего вызова», который адресует все устройства на шине. Когда используется этот адрес, все устройства в теории должны послать сигнал подтверждения. Однако устройства, которые могут обрабатывать «общий вызов», на практике встречаются редко.

Первые семь битов первого байта образуют адрес ведомого. Восьмой, младший бит, определяет направление пересылки данных. «Ноль» означает, что ведущий будет записывать информацию в выбранного ведомого. «Единица» означает, что ведущий будет считывать информацию из ведомого.

После того, как адрес послан, каждое устройство в системе сравнивает первые семь бит после сигнала СТАРТ со своим адресом. При совпадении устройство полагает себя выбранным как ведомый-приёмник или как ведомый-передатчик, в зависимости от бита направления.

Адрес ведомого может состоять из фиксированной и программируемой части. Часто случается, что в системе будет несколько однотипных устройств (к примеру, ИМС памяти, или драйверов светодиодных индикаторов), поэтому при помощи программируемой части адреса становится возможным подключить к шине максимально возможное количество таких устройств. Количество программируемых бит в адресе зависит от количества свободных выводов микросхемы. Иногда используется один вывод с аналоговой установкой программируемого диапазона адресов[1]. При этом в зависимости от потенциала на этом адресном выводе ИМС, возможно смещение адресного пространства драйвера так, чтобы однотипные ИМС не конфликтовали между собой на общей шине.

Все специализированные ИМС, поддерживающие работу в стандарте шины I²C, имеют набор фиксированных адресов, перечень которых указан производителем в описаниях контроллеров.

Комбинация бит 11110ХХ адреса зарезервирована для 10-битной адресации.

Как следует из спецификации шины, допускаются как простые форматы обмена, так и комбинированные, когда в промежутке от состояния СТАРТ до состояния СТОП ведущий и ведомый могут выступать и как приёмник, и как передатчик данных. Комбинированные форматы могут быть использованы, например, для управления последовательной памятью.

Во время первого байта данных можно передавать адрес в памяти, который записывается во внутренний регистр-защёлку. После повторения сигнала СТАРТа и адреса ведомого выдаются данные из памяти. Все решения об авто-инкременте или декременте адреса, к которому произошёл предыдущий доступ, принимаются конструктором конкретного устройства. Поэтому в любом случае лучший способ избежать неконтролируемой ситуации на шине перед использованием новой (или ранее не используемой) ИМС — следует тщательно изучить её описание (datasheet или reference manual), получив его с сайта производителя. Более того, производители часто размещают рядом более подробные инструкции по применению.

В любом случае по спецификации шины все разрабатываемые устройства должны сбрасывать логику шины при получении сигнала СТАРТ или повторный СТАРТ и подготавливаться к приёму адреса.

Тем не менее, основные проблемы с использованием I²C шины возникают именно из-за того, что разработчики, «начинающие» работать с I²C шиной, не учитывают того факта, что ведущий (часто — микропроцессор) не имеет монопольного права ни на одну из линий шины.

1. Связь процессора с памятью (чаще EEPROM)

2. HDMI и DVI интерфейсы (для передачи служебной информации от телевизора к устройству которое воспроизводит видеоконтент, либо для передачи информации от монитора к компьютеру для передачи информации, что за монитор подключили с какими характеристикаи, передача информации от термостата ЦП или информация о скорости вращения кулера и т.д.)

3. Микросхемы и карты памяти (EEPROM, RAM, FERAM, Flash);

4. Доступ к низкоскоростным ЦАП/АЦП;

5. Регулировка контрастности, насыщенности и цветового баланса мониторов;

6. Регулировка звука в динамиках;

7. Управление светодиодами, в том числе в мобильных телефонах;

8. Чтение информации с часов реального времени (кварцевых генераторов);

9. Управление включением/выключением питания системных компонент;

10. Клавиатуры

11. Информационный обмен между микроконтроллерами;

Пример системы с шиной I²C:

На рисунке (Кликабельно):

(a) Высокоинтегрированный телевизор

Микроконтроллер

ФАПЧ-синтезатор

Флеш-память

Мультисистемный декодер сигналов цветности

Стереодекодер звука

Улучшитель сигнала картинки

Hi-Fi аудиопроцессор

Аналоговый видеопроцессор

Декодер телетекста

ИМС сигналов OSD

(b) базовая станция радиотелефона стандарта DECT

Генератор DTMF

Интерфейс телефонной линии

Кодек АДИКМ

Пакетный контроллер

Микроконтроллер